ПОЗНАВАТЕЛЬНОЕ Сила воли ведет к действию, а позитивные действия формируют позитивное отношение Как определить диапазон голоса - ваш вокал Игровые автоматы с быстрым выводом Как самому избавиться от обидчивости Противоречивые взгляды на качества, присущие мужчинам Вкуснейший "Салат из свеклы с чесноком" Натюрморт и его изобразительные возможности Применение, как принимать мумие? Мумие для волос, лица, при переломах, при кровотечении и т.д. Как научиться брать на себя ответственность Зачем нужны границы в отношениях с детьми? Световозвращающие элементы на детской одежде Как победить свой возраст? Восемь уникальных способов, которые помогут достичь долголетия Классификация ожирения по ИМТ (ВОЗ) Глава 3. Завет мужчины с женщиной Оси и плоскости тела человека - Тело человека состоит из определенных топографических частей и участков, в которых расположены органы, мышцы, сосуды, нервы и т.д.

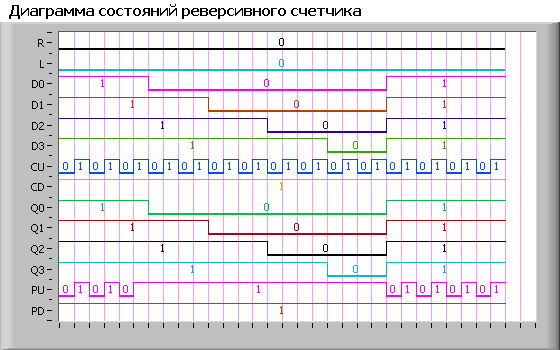

| Полный цикл работы в режиме счёта и установки. 12

Реверсивный счётчик

Схема реверсивного счетчика:

Статический режим. Режим счёта на увеличение.

Импульс на выходе PU можно зарегистрировать только по диаграмме состояний, но не по таблице истинности, т.к. состояния сигналов в таблицу истинности записываются при переходе сигнала на входе СU с 0 в 1, а импульс на выходе PU появляется в тот момент, когда на входе CU всё ещё установлен уровень лог. 0. Ксч = 16. Режим счёта на уменьшение.

Ситуация с сигналом PD аналогична той, которая была с сигналом PU.Импульс на выходе PD можно зарегистрировать только по диаграмме состояний, но не по таблице истинности, т.к. состояния сигналов в таблицу истинности записываются при переходе сигнала на входе СD с 0 в 1, а импульс на выходе PD появляется в тот момент, когда на входе CD всё ещё установлен уровень лог. 0.

Режим параллельной загрузки.

Параллельная загрузка происходит при уровне лог. «0» на входе L. Динамический режим. Режим счёта.

Сигнал PD формируется счётчиком в режиме обратного счёта при переходе счётчика из состояния 0000 в состояние 1111. Сигнал PU формируется счётчиком в режиме прямого счёта при переходе счётчика из состояния 1111 в состояние 0000.

Режимы сброса и параллельной загрузки.

По данной диаграмме видно, что счётчик переходит в режим сброса при уровне лог. 1 на входе R независимо от сигнала на входе L. Счётчик переходит в режим параллельной загрузки при уровне лог. 0 на входе L и уровне лог. 0 на входе R. Исследование выходных сигналов PU и PD.

R=1, L = x, CU = 1, CD = f

При R=1 и подаче частоты на вход CD, выход PD дублирует сигнал на входе CD.

R=0, Dx = 0, L = 0, CD = f

При R = 0, L = 0 и комбинации 0000 на входе параллельной загрузки и подаче частоты на вход CD, выход PD дублирует сигнал на входе CD. R=0, Dx = 1, L = 0, CU = f

При R = 0, L = 0 и комбинации 1111 на входе параллельной загрузки и подаче частоты на вход CU, выход PU дублирует сигнал на входе CU.

Сумматор

Сумматоры классифицируют по различным признакам. В зависимости от системы счисления различают: · двоичные; · двоично-десятичные (в общем случае двоично-кодированные); · десятичные; · прочие (например, амплитудные). По количеству одновременно обрабатываемых разрядов складываемых чисел: · одноразрядные, · многоразрядные. По числу входов и выходов одноразрядных двоичных сумматоров: · четверть сумматоры (элементы “сумма по модулю 2”; элементы “исключающее ИЛИ”), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма; · полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд); · полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд). По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на: · последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании; · параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

УГО (одноразрядного полного(двоичного)сумматора):

1 - выход суммы S1;

12 |