ПОЗНАВАТЕЛЬНОЕ Сила воли ведет к действию, а позитивные действия формируют позитивное отношение Как определить диапазон голоса - ваш вокал Игровые автоматы с быстрым выводом Как самому избавиться от обидчивости Противоречивые взгляды на качества, присущие мужчинам Вкуснейший "Салат из свеклы с чесноком" Натюрморт и его изобразительные возможности Применение, как принимать мумие? Мумие для волос, лица, при переломах, при кровотечении и т.д. Как научиться брать на себя ответственность Зачем нужны границы в отношениях с детьми? Световозвращающие элементы на детской одежде Как победить свой возраст? Восемь уникальных способов, которые помогут достичь долголетия Классификация ожирения по ИМТ (ВОЗ) Глава 3. Завет мужчины с женщиной Оси и плоскости тела человека - Тело человека состоит из определенных топографических частей и участков, в которых расположены органы, мышцы, сосуды, нервы и т.д.

| Транзисторно-транзисторная логика (ТТЛ)

Лекция №3 Транзисторные ключи Моп и Кмоп Логические элементы - это устройства, реализующие логические функции. Рассмотрим логические элементы на транзисторах. С целью понимания работы схем, мы можем предполагать, что элементарный транзистор представляет собой электронный ключ. На рисунке 1.1(a) представлен подобный ключ, управляемый логическим сигналом x. Когда сигнал x низкого уровня – ключ открыт, а когда высокого – закрыт. Наиболее популярный тип транзистора для реализации электронного ключа – полевой транзистор структуры метал-окисел-полупроводник (МОП-транзистор). Имеются два различных типа МОП-транзисторов, известные как n-канальные МОП-транзисторы, сокращенно NMOS, и р-канальные – обозначаемые как PMOS. Условное обозначение для n-канального МОП-транзистора представлено на рисунке 1.1(б). Транзистор имеет четыре вывода, называемых истоком (Source), стоком (Drain), затвором (Gate) и подложкой (Substate or Body). В логических схемах подложка обычно соединена с выводом GND.

(б) n-канальный МОП-транзистор

(в) упрощенное обозначение для n-канального МОП-транзистора Рисунок 1.1 — n-канальный МОП-транзистор в режиме ключа

Работа транзистора управляется напряжением VG, прикладываемым к затвору. Если сигнал VG низкого уровня , то проводящий канал между истоком и стоком отсутствует, и мы говорим, что транзистор заперт. Если сигнал VG высокого уровня – транзистор открыт и соединяет между собой сток и исток посредством образовавшегося проводящего канала. Принцип действия транзистора p-канальной архитектуры отражен на рисунке 1.2(а). Условное обозначение приведено на рисунке 1.2(б). В логических схемах затвор транзистора всегда соединяется с выводом VDD схемы. Поэтому на практике обычно используется его упрощенное обозначение, представленное на рисунке 1.2(в). Если сигнал VG высокого уровня, то транзистор заперт. Когда VG низкого уровня, транзистор открыт и работает подобно замкнутому ключу, подключающего исток к стоку.

(б) p-канальный МОП-транзистор

(в) упрощенное обозначение p-канального МОП-транзистора Рисунок 1.2 — p-канальный МОП-транзистор в режиме ключа Логические элементы МОП Первые схемные реализации логических элементов с использованием МОП-транзисторов стали популярными в 1970-х и опирались либо на использование p-канальных МОП-транзисторов, либо на использование n-канальных МОП-транзисторов, но не оба этих типа одновременно. С начала 1980-ых NMOS и PMOS-транзисторы стали использоваться совместно. Вначале рассмотрим реализацию логических элементов с использованием NMOS-транзисторов. Такие цепи обычно называют NMOS-цепями. Затем будут рассмотрены схемы, использующие как NMOS, так и PMOS-транзисторы, и объединенные в отдельную технологию, известную как КМОП-структура (комплиментарная МОП), или CMOS. На рисунке 1.4(а) представлена принципиальная электрическая схема, в которой положительный вывод источника питания показан стрелкой и обозначен VDD, а отрицательный вывод источника питания обозначен как GND. Отметим, что на практике чаще всего используется именно такое обозначение, поэтому будем придерживаться его и мы. Когда сигнал Vx=0V, NMOS транзистор закрыт. Поэтому ток через резистор R отсутствует, и на выходе Vf=5V. С другой стороны, когда Vx=5V, транзистор открыт и на выходе Vf устанавливается низкий уровень напряжения. Точное значение напряжения на выходе Vf в этом случае зависит от величины тока, протекающего через резистор и транзистор. Как правило, уровень Vf составляет около 0.2V. Если представить значение сигнала Vf как функцию от сигнала Vx, то данная схема работает как инвертор. В схемотехнике такая функция обозначается как f = x, к.

Рисунок 1.4 — Инвертор, реализованный с использованием NMOS-технологии Использование резистора в схеме инвертора обусловлено необходимостью ограничить ток, протекающий в цепи при Vx=5V. В интегральной схемотехнике в качестве такого ограничителя обычно используется транзистор. Используя последовательное соединение NMOS-транзисторов, как показано на рисунке 1.5(a), можно реализовать логический элемент И-НЕ. Если Vx1=Vx2=5V, оба транзистора будут открыты и Vf будет равен 0V. Но если либо Vx1, либо Vx2=0, то ток в цепи будет отсутствовать и Vf будет равен 5V.

Рисунок 1.5 — Реализация элемента И-НЕ на NMOS-транзисторах

Параллельное соединение NMOS-транзисторов приведено на рисунке 1.6(a). Здесь, если либо Vx1=5V, либо Vx2=5V, то Vf будет равен 0V. Только если Vx1 и Vx2 будут равны 0V одновременно, то Vf будет равен 5V. Соответствующая таблица истинности приведена на рисунке 1.6(а). Отметим, что данная схема реализует логическую функцию ИЛИ-НЕ. Ее условные графические обозначения приведены на рисунке 1.6(б).

Рисунок 1.6 — Реализация элемента ИЛИ-НЕ на NMOS-транзисторах

Для реализации чистых элементов ИЛИ и И с использованием NMOS-транзисторов применяют последовательное соединение элементов ИЛИ-НЕ и И-НЕ с инвертором. На рисунках 1.7 и 1.8 представлена реализация элементов И и ИЛИ соответственно.

Рисунок 1.7 — Реализация элемента И на NMOS-транзисторах

Рисунок 1.8 — Реализация элемента ИЛИ на NMOS-транзисторах Логические элементы КМОП Эквивалентные схемы элементов, представленных выше, можно получить, используя только PMOS-транзисторы. Однако наибольший интерес представляет совместное применение PMOS и NMOS-транзисторов. Такая технология наиболее популярна сегодня и называется CMOS-технологией. Она обеспечивает максимальное быстродействие работы элементов при низком энергопотреблении по сравнению со всеми другими технологиями. В NMOS-цепях логические функции реализовались комбинацией соединений NMOS-транзисторов, объединенных с токоограничивающим элементом. Т.к. все элементы, построенные на NMOS-транзисторах реализуют отрицательные функции (НЕ, ИЛИ-НЕ, И-НЕ), то их можно условно представить так, как показано на блок-схеме рисунка 1.9.

Рисунок 1.9 — Структура NMOS-схемы

При этом все транзисторные цепи объединены в блок PDN (Pull-down Network) – блок отрицательной логики. Для реализации прямых логических функций необходимо соединение двух отрицательных элементов, что снижает быстродействие всего элемента в целом. Концепция CMOS-цепей основана на реализации прямых функций (И, ИЛИ) на PMOS-транзисторах таким образом, что блоки прямой логики (PUN – Pull-up Network) и блоки отрицательной логики (PDN — Pull-down Network) являются дополнениями друг друга. Тогда логическая схема, реализующая типичный логический элемент, будет иметь вид, представленный на рисунке 1.10.

Рисунок 1.10 — Структура CMOS-схемы

Для любой комбинации входных сигналов PDN устанавливает уровень логического нуля на выходе Vf , или PUN устанавливает на этом выходе уровень логической единицы. PDN и PUN имеют равное количество транзисторов, которые размещены так, что эти два блока работают параллельно. Там, где PDN включает NMOS-транзисторы, соединенные последовательно, PUN строится на PMOS-транзисторах, соединенных параллельно, и наоборот. Самый простой пример CMOS-схемы — инвертор, показан на рисунке 1.11.

Рисунок 1.11 — Реализация CMOS-инвертора

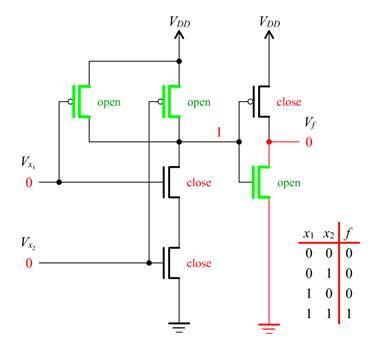

Когда сигнал Vx=0V, транзистор T2 закрыт, а транзистор T1 открыт. Следовательно, Vf=5V, и так как T2 закрыт, ток через транзисторы не течет. Когда Vx=5V, то T2 открыт, а T1 закрыт. Таким образом, Vf=0V, и тока в цепи по прежнему не будет, т.к. транзистор T1 закрыт . Это свойство справедливо для всех CMOS-цепей – логические элементы практически не потребляют ток в статическом режиме. Ток в таких цепях будет протекать только во время переключения элементов (вот почему, с ростом частоты работы устройств, построенных по этой технологии, возрастает и энергопотребление). Вследствие этого, CMOS-схемы стали наиболее популярной технологией при реализации цифровых логических устройств. Рисунок 1.12 представляет принципиальную электрическую схему логического элемента И-НЕ CMOS. Реализация этого элемента подобна NMOS-схеме, представленной на рисунке 1.5 за исключением того, что токоограничивающий резистор был заменен блоком PUN, состоящим из двух PMOS-транзисторов, соединенных параллельно. Таблица истинности на рисунке показывает состояние каждого из этих четырех транзисторов для каждой логической комбинации вводов x1 и x2. Легко проверить, что данная схема реализует логическую функцию И-НЕ. В статическом состоянии отсутствует путь для протекания тока от VDD к Gnd.

Рисунок 1.12 — CMOS-реализация логического элемента И-НЕ

Схема на рисунке 1.12 может быть получена исходя из логического выражения, которое определяет логическую функцию И-НЕ,

Таким образом f = 1, когда либо вход x1, либо вход x2 имеют значение логического нуля, что означает что PUN должен иметь два PMOS-транзистора, соединенных параллельно. Блок PDN должен дополнять функцию f, которая имеет вид: f = x1x2 Функция f = 1, когда оба входа x1 и x2 равны 1, поэтому блок PDN должен иметь два NMOS-транзистора, соединенных последовательно. Схема для CMOS-реализации элемента ИЛИ-НЕ может быть получена из логического выражения:

Функция f = 1 в том случае, если x1 и x2 равны 0 одновременно. Тогда PUN состоит из двух PMOS-транзисторов, соединенных последовательно. Блок PDN, который реализует функцию f = x1 + x2, состоит из двух NMOS-транзисторов, соединенных параллельно, что и показано на рисунке 1.13.

Рисунок 1.13 — CMOS-реализация логического элемента ИЛИ-НЕ

Элемент И в CMOS-реализации представляет собой последовательное соединение логического элемента И-НЕ и инвертора, как показано на рисунке 1.14. Точно так же элемент ИЛИ строится путем соединения элемента ИЛИ-НЕ с инвертором.

Рисунок 1.14 — CMOS-реализация элемента И

Транзисторно-транзисторная логика (ТТЛ)

На рисунке 2.1 изображена схема ТТЛ. Если все входные напряжения имеют высокий уровень, ток, проходящий через резистор R1 по открытому в прямом направлении переходу база-коллектор входного транзистора, течет в базу транзистора Т2 и приводит его в открытое состояние. При этом напряжение на коллекторе входного транзистора составляет около 0,6 В. Если на один из входов подано низкое напряжение, то соответствующий переход база-эмиттер открывается и отбирает базовый ток транзистора Т2. При этом транзистор Т2 запирается и выходное напряжение принимает значение, соответствующее высокому уровню.

Рисунок 2.1 — Принцип построения элемента И-НЕ типа ТТЛ

Известно, что в каждом транзисторе коллектор с эмиттером можно поменять местами. При этом переход база-коллектор оказывается включенным в прямом направлении, а переход база-эмиттер – в обратном. Этот способ включения транзистора называется инверсным. Инверсное включение отличается от прямого лишь незначительной величиной коэффициента усиления по току, который в данном случае будем называть коэффициентом усиления по току для инверсного включения. Итак, ток эмиттера равен IE = ВинвIB1 Коэффициент усиления по току обычного транзистора, включенного инверсно, составляет около 10. Следовательно, в данном случае это приводит к недопустимо большой величине входного тока. Однако в многоэмиттерном транзисторе применяется особая геометрия р-n-перехода, с помощью которой коэффициент усиления по току для инверсного включения снижается почти до 0,1. Многоэмиттерные транзисторы отдельно не выпускаются, а используются только в интегральных схемах. В интегральных схемах ТТЛ транзистор Т2 заменяется, как правило, выходным каскадом, который имеет больший выходной ток, или, иначе говоря, обеспечивает более высокий запас помехоустойчивости для логического нуля. Такая схема показана на рисунке 2.2. Если транзистор Т2 закрыт, то потенциал его эмиттера равен нулю и транзистор Т3 также закрыт. Через эмиттерный повторитель Т4 на выход схемы подается высокий уровень напряжения. Благодаря эмиттерному повторителю выход схемы в единичном состоянии также является низкоомным и обладает высокой нагрузочной способностью.

Рисунок 2.2 — Элемент И-НЕ типа ТТЛ

Если транзистор Т2 открыт, падение напряжения на нем мало. При этом базовый ток транзистора Т3 достигает такой величины, что он остается в состоянии насыщения даже при больших значениях выходного тока. Выходное напряжение составляет в этом случае около 0,1 В. Потенциалы баз транзисторов Т3 и Т4лежат в интервале 0,6-0,7 В. Чтобы предотвратить открытие транзистора Т4 при нулевом сигнале на выходе, включается диод D. Однако в момент переключения схемы на короткое время открываются оба транзистора. В этом случае потребление тока ограничивается только защитным резистором R4. Такой импульс тока вызывает высокочастотные помехи на шине питания и общей шине. Для устранения этого эффекта используются низкоомные шины питания и конденсаторы для сглаживания питающего напряжения.

|

. Это выражение определяет состояния, при которых f = 1; следовательно, оно определяет поведение блока PUN. Так как этот блок состоит из PMOS-транзисторов, которые открываются при подаче на их входы логического нуля, входная переменная xi открывает транзистор, если xi=0. По правилу де Моргана мы имеем:

. Это выражение определяет состояния, при которых f = 1; следовательно, оно определяет поведение блока PUN. Так как этот блок состоит из PMOS-транзисторов, которые открываются при подаче на их входы логического нуля, входная переменная xi открывает транзистор, если xi=0. По правилу де Моргана мы имеем: