ПОЗНАВАТЕЛЬНОЕ Сила воли ведет к действию, а позитивные действия формируют позитивное отношение Как определить диапазон голоса - ваш вокал Игровые автоматы с быстрым выводом Как самому избавиться от обидчивости Противоречивые взгляды на качества, присущие мужчинам Вкуснейший "Салат из свеклы с чесноком" Натюрморт и его изобразительные возможности Применение, как принимать мумие? Мумие для волос, лица, при переломах, при кровотечении и т.д. Как научиться брать на себя ответственность Зачем нужны границы в отношениях с детьми? Световозвращающие элементы на детской одежде Как победить свой возраст? Восемь уникальных способов, которые помогут достичь долголетия Классификация ожирения по ИМТ (ВОЗ) Глава 3. Завет мужчины с женщиной Оси и плоскости тела человека - Тело человека состоит из определенных топографических частей и участков, в которых расположены органы, мышцы, сосуды, нервы и т.д.

| Последовательностные схемы. 12

Коэффициент разветвления по выходу. Коэффициент разветвления по выходу наиболее часто используемый параметр. Определяется отношением выходного тока

Рассмотрим соединение инвертора с другими.

Рис.2

Количество элементов, которое можно подключить:

Iin – входной ток.

(N – либо число выводов, либо число схем, подключаемых к выходу.)

Различают:

коэффициент разветвления по выходу с низким уровнем входного сигнала(«0»).

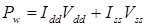

Следующие параметры: Мощность рассеяния. Для оценки мощности рассчитывают произведение тока через источник питания на уровень напряжения питания в соответствующем логическом состоянии и усредняют в каждом логическом состоянии.

Рис.3 Где:

Среднее значение:

Если 2 источника: расчет делаем для каждого источника и усредняем. Чем меньше Еще один рассматриваемый параметр.

PDàPower-Delay.

2) Последовательностные схемы. Последовательностные устройства - объекты, состояние на выходе которых определяется не только входными сигналами, но и промежуточным состоянием входных узлов, зависящих от комбинаций сигналов предшествовавших рассматриваемому состоянию. К ним относят: триггеры, счетчики, регистры и т.д. По виду входных сигналов различают: 1)СТАТИЧЕСКИЕ; 2)ДИНАМИЧИСКИЕ(выходной уровень определяется серией импульсов).

По способу управления: 1)СИНХРОНЫЕ(в фиксированный момент времени); 2)АСИНХРОНЫЕ(в любой момент времени). Общая схема триггера показана на Рис.1.

S – SET R – RESET J – JERK K – KILL D – DELAY Управляющие сигналы: S – установка на выходе по каналу Q “1”; R – установка на выходе по каналу Q “0”; J – установка по каналу Q “1”; K – установка по каналу Q “0”; При подаче J = K = 1 на выходе логическое состояние меняется. Q - выполняют роль задержки(для задержки сигнала на такт). T – изменяет сигнал на выходе на противоположный при подаче тактового сигнала. С – сигнал синхронизации, разрешает или запрещает изменение состояния триггера. Пример на RS-триггере: Карта Карно показана на Рис.2:

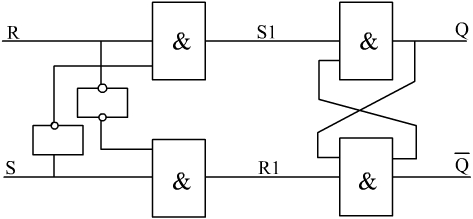

В базисе ИЛИ-НЕ Рис.3: В базисе И-НЕ Рис.4:

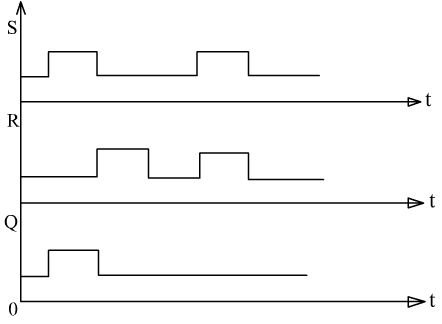

Построим диаграмму в базисе ИЛИ-НЕ, на Рис.5:

X -запрещенное состояние

Диаграмма в базисе И-НЕ показана на Рис.6:

Рассмотрим триггеры R,S,E. Общие назначение триггеров - снять неопределенность при одновременной подаче сигналов на вход. Рассмотрим R-триггер. Схема показана на Рис.7.

В рассмотренной схеме снятие неопределенности обеспечивается блокировкой сигнала S с помощью схемы И-НЕ, на входы которой поступают: первый вход – S, второй вход – R.

Рассмотрим S – триггер, схема показана на Рис.9.

Для перевода RS-триггера в S-триггер, обратная связь с канала S заводится на вход R.

D-триггер Назначение D-триггеров – передача информации с задержкой. Функциональная схема D-триггера приведена на рисунке 1:

Рис 1. На рисунке 2 изображено условное обозначение D-триггера:

Рис 2. Временная диаграмма D-триггера показана на рисунке 3:

Рис 3.

12 |

ко входному

ко входному  по логическому состоянию (N- целое число, округленное до меньшего значения).

по логическому состоянию (N- целое число, округленное до меньшего значения).

где: Iout – выходной ток,

где: Iout – выходной ток, коэффициент разветвления по выходу с высоким уровнем входного сигнала(«1»)

коэффициент разветвления по выходу с высоким уровнем входного сигнала(«1»)

- потреблен при логической “1” на выходе;

- потреблен при логической “1” на выходе; - потреблен при логической “0” на выходе ;

- потреблен при логической “0” на выходе ;

, тем лучше схема (не всегда).

, тем лучше схема (не всегда). - произведение времени распространения сигнала(

- произведение времени распространения сигнала(  ) на мощность рассеивания(

) на мощность рассеивания(  ).

).

Диаграмма будет иметь следующий вид Рис.8:

Диаграмма будет иметь следующий вид Рис.8: - в точке 4 переводит состояние выхода схемы “И” (S1) в состояние с уровнем “1”, который не меняет состояние выхода схемы “И-НЕ” по каналу Q. Сигнал R1=0 в момент 4 поступая на вход

- в точке 4 переводит состояние выхода схемы “И” (S1) в состояние с уровнем “1”, который не меняет состояние выхода схемы “И-НЕ” по каналу Q. Сигнал R1=0 в момент 4 поступая на вход  , переводит

, переводит

Построим диаграмму, показана на Рис.10:

Построим диаграмму, показана на Рис.10: Рассмотрим E-триггер, схема на Рис.11:

Рассмотрим E-триггер, схема на Рис.11: Построим диаграмму, показана на Рис.12.

Построим диаграмму, показана на Рис.12.

Особенностью данной схемы является блокировка сигнала по каналу D и передача управления на канал С. В момент времени 1 (см. рисунок 3) на выходе D1 формируется нулевой уровень сигнала в соответствии с работой логического элемента «и-не». Нулевой уровень сигнала переводит канал С1 в состояние логической единицы, и соответственно на выходе Q также формируется уровень единицы. В момент времени когда D становится равным 0, а C имеет уровень единицы, на выходе D1 формируется единичный уровень который в сочетании с единичным уровнем сигнала С переводит выход Q в состояние единицы. Рассмотренной схеме присущ недостаток – эффект сквозного управления. Для устранения этого недостатка используют синхронизацию по фронту.

Особенностью данной схемы является блокировка сигнала по каналу D и передача управления на канал С. В момент времени 1 (см. рисунок 3) на выходе D1 формируется нулевой уровень сигнала в соответствии с работой логического элемента «и-не». Нулевой уровень сигнала переводит канал С1 в состояние логической единицы, и соответственно на выходе Q также формируется уровень единицы. В момент времени когда D становится равным 0, а C имеет уровень единицы, на выходе D1 формируется единичный уровень который в сочетании с единичным уровнем сигнала С переводит выход Q в состояние единицы. Рассмотренной схеме присущ недостаток – эффект сквозного управления. Для устранения этого недостатка используют синхронизацию по фронту.