ПОЗНАВАТЕЛЬНОЕ

| Віднімаючі двійкові лічильники 12

У віднімаючих лічильниках кожний черговий рахунковий імпульс зменшує результат рахунку на одиницю, тобто забезпечується зворотний рахунок. Зміна напряму рахунку при побудові лічильника на базі тригерів, аналогічних застосованим в п. 1.1, досягається зміною характеру міжрозрядних з'єднань – вхід (i+1) -го розряду сполучений з прямим виходом i-го розряду.

Рис. 2. Віднімаючий двійковий отирьохрозрядний лічильник: а)схема; б) часові діаграми

З часових діаграм виходить, що перший з послідовності рахункових імпульсів встановлює всі тригери в одиничний стан (N=Nmax=15). Кожний подальший рахунковий імпульс зменшує результат рахунку на одиницю. Місткість лічильника рівна 16, отже, 16-й рахунковий імпульс знов встановить всі тригери в одиничний стан. Часові діаграми (рис. 2, б) зображені з урахуванням затримок, що вносяться тригерами (час, необхідний для перемикання тригера). Їх аналіз дозволяє визначити динамічні параметри лічильника: час проходження tсл.=4t, де t - час перемикання тригера, а також час реєстрації tр=4t, відповідне найтривалішому перехідному процесу – переходу лічильника з стану 0000 в стан 1111.

Реверсивні двійкові лічильники Порівняння двох розглянутих вище схем двійкових лічильників показує, що для переходу від режиму підсумовування до режиму віднімання необхідно вхід 2, 3 ., n-го тригера перемкнути від інверсного до прямого виходу попереднього тригера. Тому для побудови схеми реверсивного лічильника між його розрядами достатньо включити одну з приведених на рис. 3 комутуючих ланцюгів.

Рис. 3. Варіанти комутації між розрядних зв’язків.

Для обох варіантів значення вхідного сигналу (i+1) -го розряду

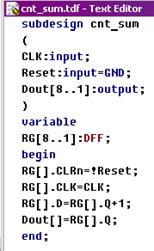

Рис. 4. Схема реверсивного лічильника Методичний приклад Напишемо програму в AHDL для 4-х розрядного двійкового лічильника, що підсумовує(рис. 5) Clk – тактовий вхід, Reset ̶ вхід асинхронного скидання лічильника в нуль Dout[4..1] ̶ 4-х розрядний вихід лічильника

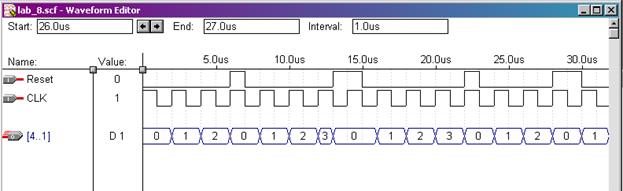

Рис. 5 - Лічильник в AHDL, що підсумовує Відобразимо діаграму роботи лічильника(рис. 6)

Рис. 6 – Діаграма роботи лічильника Для віднімача програма роботи буде дещо іншою(рис. 8): Clk – тактовий вхід, Reset ̶ вхід асинхронного встановлення лічильника Dout[4..1] ̶ 4-х розрядний вихід лічильника

Рис. 5 - Лічильник в AHDL

3. Завдання на лабораторну роботу Таблиця 1

3.1. Досліджувати роботу двійкового лічильника(розрядність взяти з табл.1), що підсумовує. 3.1.1. Написати програму в AHDL для двійкового лічильника, що підсумовує (рис. 1). 3.1.2. Подати на вхід лічильника послідовні 16 рахункових імпульсів і проконтролювати стан лічильника після подачі кожного чергового рахункового імпульсу. 3.1.3. Показати діаграму роботи лічильника 3.2. Досліджувати роботу віднімаючого двійкового лічильника. 3.2.1. Написати програму в AHDL для віднімаючого двійкового лічильника (рис. 2) і виконати дії, аналогічні п.п. 3.1.2 - 3.1.4. 3.3. Досліджувати роботу реверсивного лічильника. 3.3.1. Написати програму в AHDL для реверсивного лічильника (рис. 4) і виконати дії, аналогічні п.п. 3.1.2 - 3.1.4. 3. Зміст звіту У звіті по кожному пункту завдання повинні бути приведені: схема; часові діаграми , що пояснює роботу досліджуваного лічильника. 5. Контрольні запитання 1. Дайте визначення цифрового лічильника. 2. У якому випадку цифровий лічильник іменують двійковим? 3. Зобразіть часові діаграми, що пояснюють роботу асинхронного Т-тригера. 4. На основі ІС JK-трігерів спроектувати схеми трьохрозрядних а) підсумовуючого, б) віднімаючого лічильників. 5. Замініть тригери, що використовуються в схемі лічильника (рис. 1) на D-тригери, тактовані зрізом синхроімпульса, і побудуйте часові діаграми для модернізованої схеми лічильника. Зробіть висновки. 6. Дії, аналогічні вказаним в питанні 5, проведіть для схеми віднімаючого двійкового лічильника (рис. 2). 12 |

Отже, вибором значення управляючого сигналу V (1 або 0) забезпечується передача на вхід (i+1) -го розряду сигналу Qi або, і таким чином вживання лічильника в режимі підсумовування (V=1)або віднімання (V=0). На рис. 4 приведена побудована за вказаним принципом схема чотирьохрозрядного реверсивного лічильника.

Отже, вибором значення управляючого сигналу V (1 або 0) забезпечується передача на вхід (i+1) -го розряду сигналу Qi або, і таким чином вживання лічильника в режимі підсумовування (V=1)або віднімання (V=0). На рис. 4 приведена побудована за вказаним принципом схема чотирьохрозрядного реверсивного лічильника.